芯片堆疊技術能否實實在在解決國產芯片難題?

發布時間:2022-12-26 08:35:30 瀏覽:249次 責任編輯:騰盛精密

芯片堆疊技術作為一個新的概念,其在近幾年成為半導體領域研究熱點,但這一技術是否能夠為國產芯片發展帶來實質性的改變呢?

華為芯片堆疊技術之路

眾所周知,CPU是一個超大規模的集成電路板,指甲蓋兒大小的芯片上安置著數以億計的晶體管,再也留不出任何空白的地方,那為何不再疊加一張紙放在它的上面呢?3D堆疊由此產生。

所謂的3D堆疊技術其實很好理解,就是在原本的封裝體里面,封裝進兩個以上不同功能的芯片,一般都是在不改變原本的封裝體積大小,而在垂直方向進行的芯片疊放。

這種技術所帶來的特點就是改變了原有的在單位面積上不斷增加晶體管的方式,而是在垂直方向上進行芯片疊放,自然也會實現芯片的功能多樣化。

早在2012年,華為便已經對芯片堆疊技術進行專利公開,該專利為“芯片堆疊封裝結構”(申請公布號:CN102693968A),主要設計芯片封裝技術領域,實現芯片的高密度堆疊,提高芯片堆疊封裝結構的散熱效率。

其后幾年,華為也在不斷對外公開其芯片堆疊的相關技術,足以證明長期以來華為都在這項技術上深耕研發。

比如近幾年,華為所公布的兩項芯片堆疊相關專利,一項是“一種多芯片堆疊封裝及制作方法”(申請公布號:CN114287057A),解決因采用硅通孔技術而導致的成本高的問題。

另一項為“芯片堆疊封裝結構及其封裝方法、電子設備”(申請公布號:CN114450786A),用于解決如何將多個副芯片堆疊單元可靠的鍵合在同一主芯片堆疊單元上的問題。

▲華為專利 (來源:國家知識產權官網)

其實說到底,堆疊芯片就是利用先進的封裝技術去繞開EUV的“緊固”,放出高性能的芯片。多項與芯片堆疊相關專利的公開,或許也揭露了華為未來在芯片技術上的一個發展方向。

目前,3D芯片技術的類別包括:基于芯片堆疊的3D技術,基于有源TSV的3D技術,基于無源TSV的3D技術,以及基于芯片制造的3D技術。

3D堆疊應用商業化普及

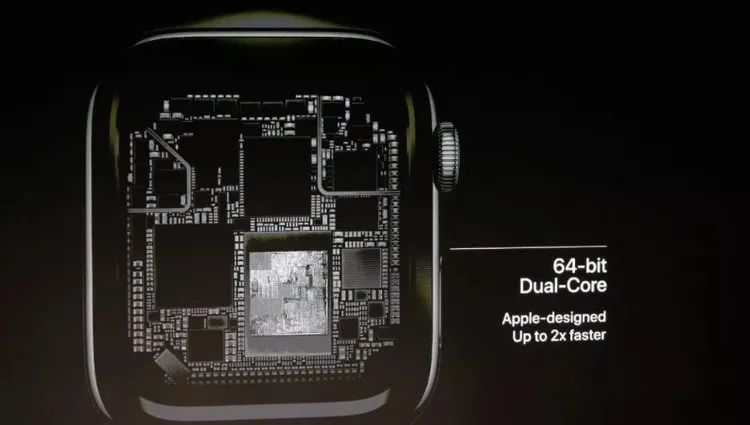

蘋果此前已經向我們證明,芯片堆疊技術是可以大幅提升處理器的性能的。前不久發布的M1 Ultra芯片,就是通過兩塊M1 Max芯片封裝而來的。

M1 Ultra將兩枚M1 Max中隱藏的芯片間互連模塊(die-to-die connector)通過技術手段整合在一起,蘋果將其稱之為“Ultra Fusion”架構,擁有1萬多個信號點,互連帶寬高達2.5TB/s,而且延遲、功耗都非常低。

這種堆疊方式可在性能、能耗和功能上帶來各種意想不到的好處。

沒有這種技術,蘋果智能手表Apple Watch也就無法做出來,三星最先進的固態存儲器、來自英偉達和谷歌的人工智能系統和索尼超級快速的新型相機也不例外。

芯片堆疊也帶來了一些全新的功能。有的手機攝像頭將圖像傳感器直接疊加在處理圖像的芯片上面。額外的速度意味著,它們能夠對照片進行多次曝光,并將其融合在一起,在昏暗的場景里捕捉到更多的光線。

3D堆疊式芯片的普及非常快速,它們也必然會成為行業主流。10年前,該技術幾乎僅僅存在于高校實驗室;五六年前,還難以找到它的商業化案例。但它如今如雨后春筍般涌現,出現在各類的應用上,如網絡化、高性能計算和Apple Watch等高端可穿戴設備。

芯片堆疊關鍵工藝及局限性

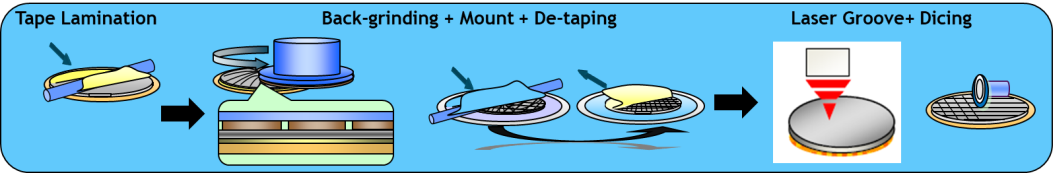

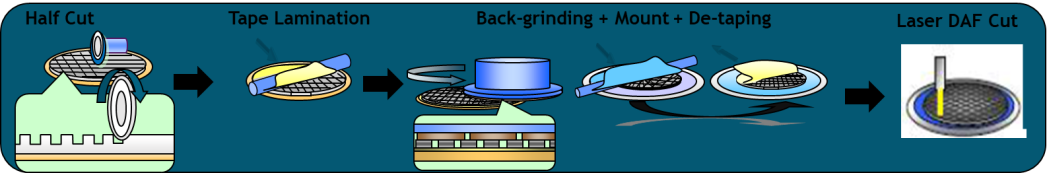

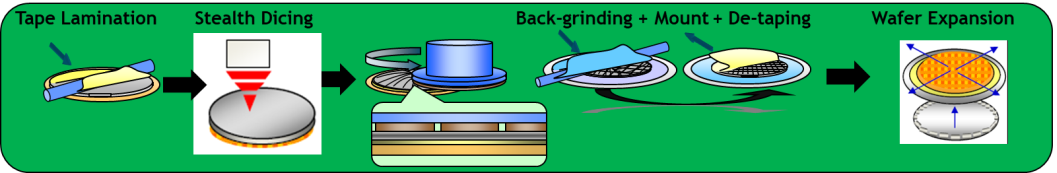

▲SDBG(來源:DISCO)

芯片堆疊技術推動國產芯片量產

在諸多限制和封鎖下,我國一直缺乏半導體關鍵設備EUV光刻機,這就導致中國在推進7nm工藝乃至更先進的工藝方面始終無法突破,但是中國芯片行業采取了兩條路線齊步走的方式發展芯片。

其中一條路線就是積極推進國產芯片制造產業鏈的完善和技術升級;另一條路線則是研發先進的封裝技術,例如華為芯片堆疊技術將兩枚同樣以14nm工藝生產的芯片堆疊在一起,從而取得接近7nm工藝的性能。

▲Kirin芯片(來源:網絡)

堆疊技術并非新技術,華為此項專利只是其中一個堆疊方法的專利展示。至少為國內被芯片“卡脖子”提出了解決方案之一,在此研發過程所沉淀和積累下來的研發能力、研發隊伍、研發平臺也是有價值的。

Tensun騰盛作為在半導體封測領域有著十六年經驗的精密裝備供應商,也一直不斷探索SiP先進封裝領域產品設備的開發和制程應用,致力于為客戶提出半導體制程封測的解決方案。

只要有市場,中國芯片就能引領世界,芯片堆疊技術能最大化發揮目前的國產芯片資源優勢。5G技術融入到各行各業,幫助傳統企業快速轉型升級,利用我們自身的優勢去提高行業發展。

————

聲明:本文部分內容參考出處有:

1.「華為公布芯片新專利,堆疊封裝的利與弊各是什么?」,來源:物聯網智庫

2.「華為首次公開芯片堆疊封裝技術!」,來源:云腦智庫

3.「一文解析多芯片堆疊封裝技術」,來源:電子發燒友

如有侵權等行為,可聯系我方刪除。

深圳市騰盛精密裝備股份有限公司

深圳市騰盛精密裝備股份有限公司